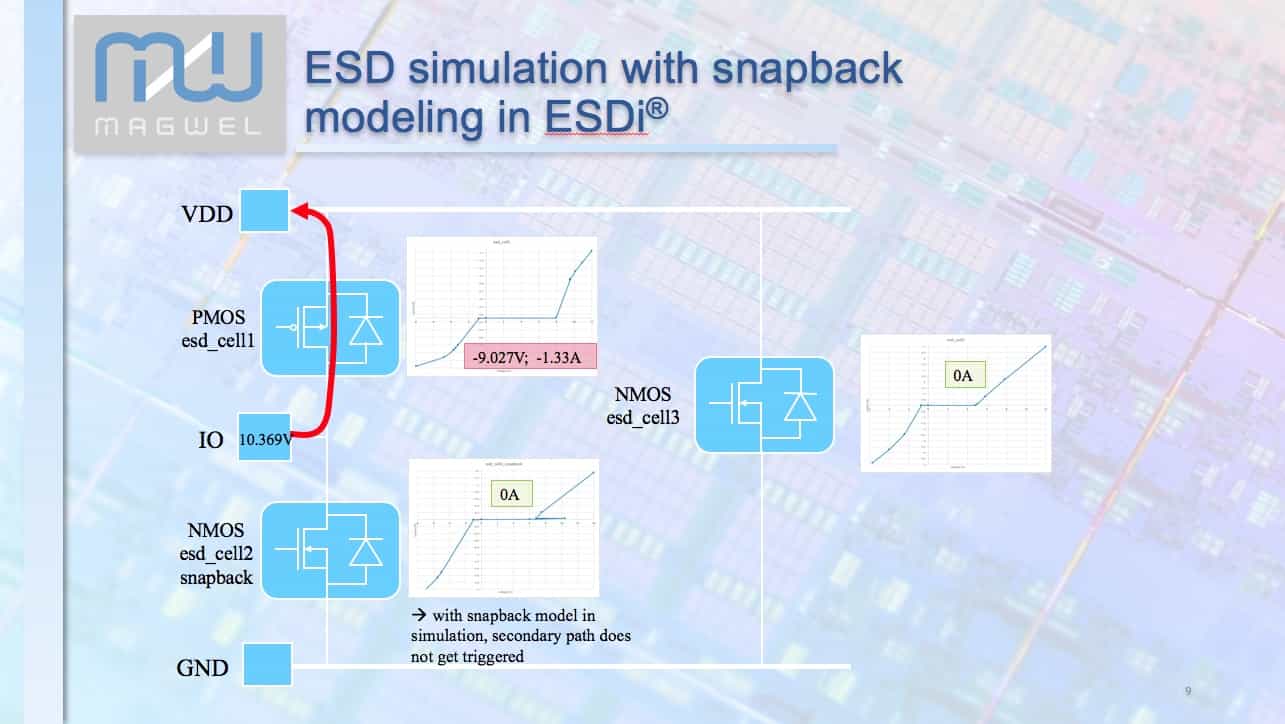

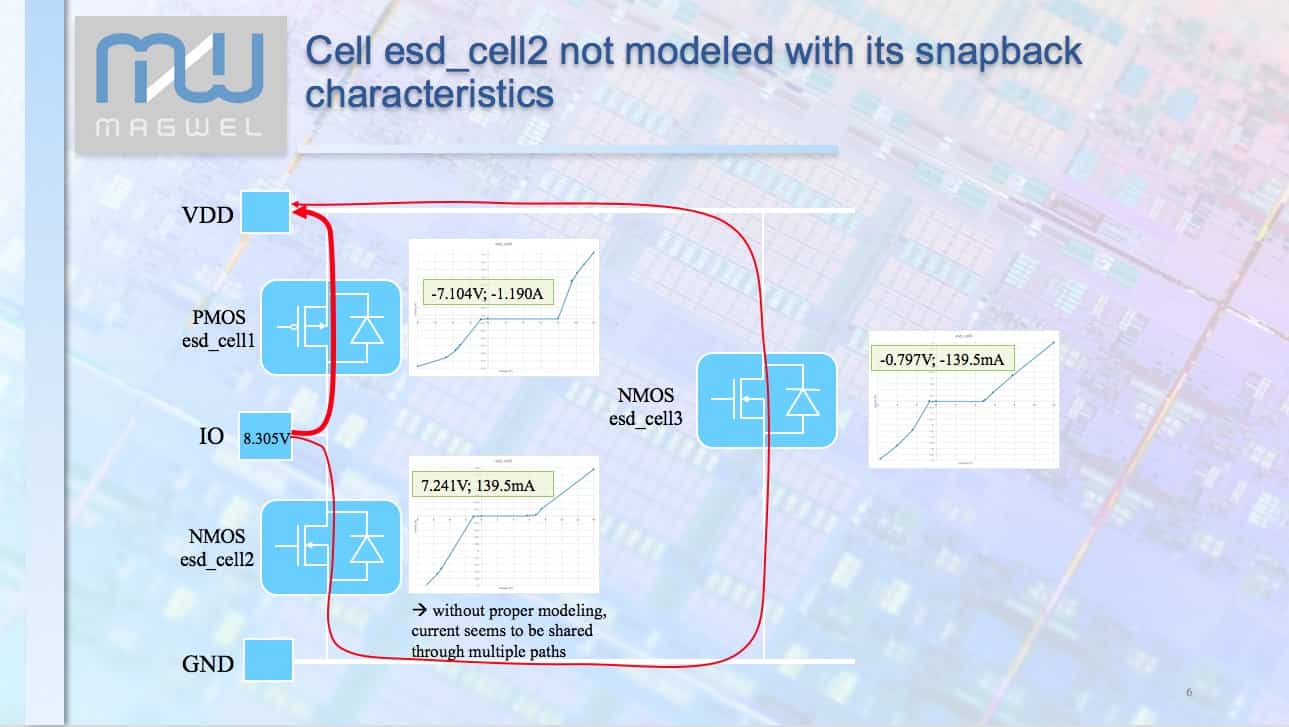

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar

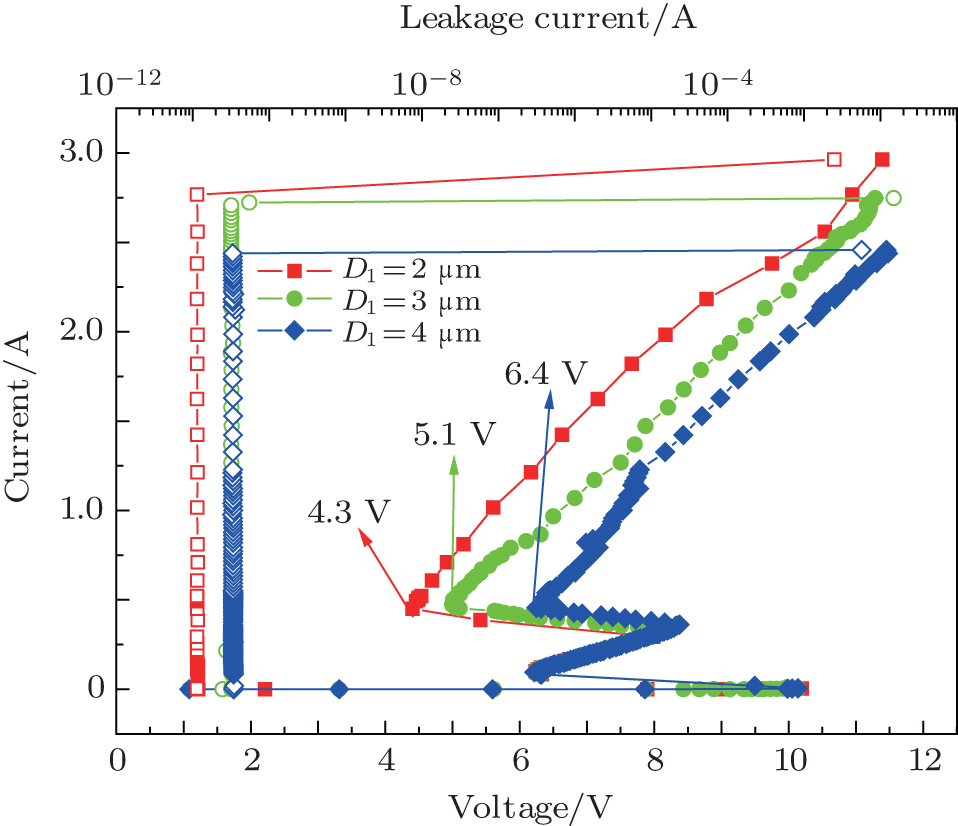

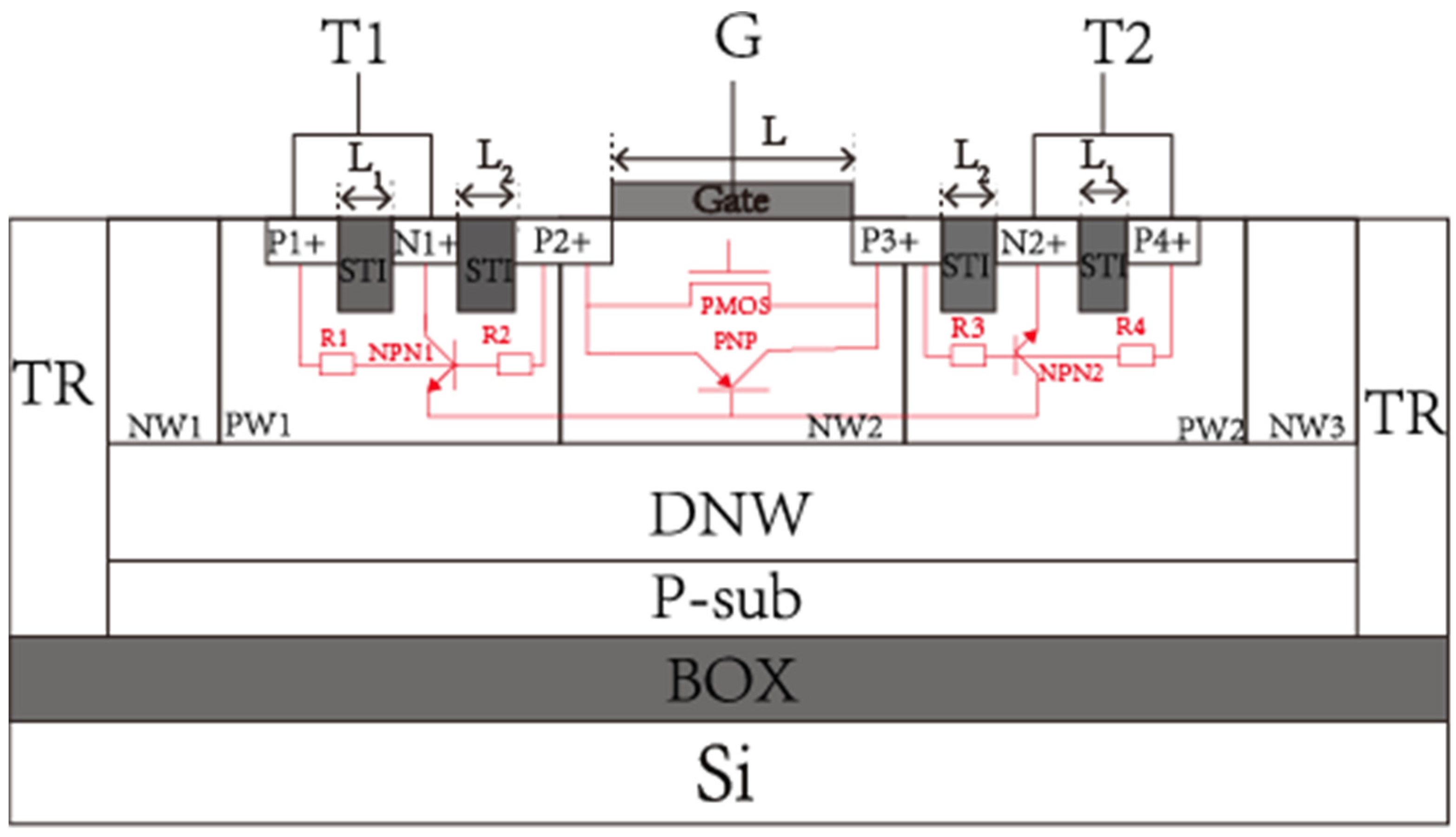

Electronics | Free Full-Text | The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

Snapback breakdown ESD device based on zener diodes on silicon-on-insulator technology - ScienceDirect

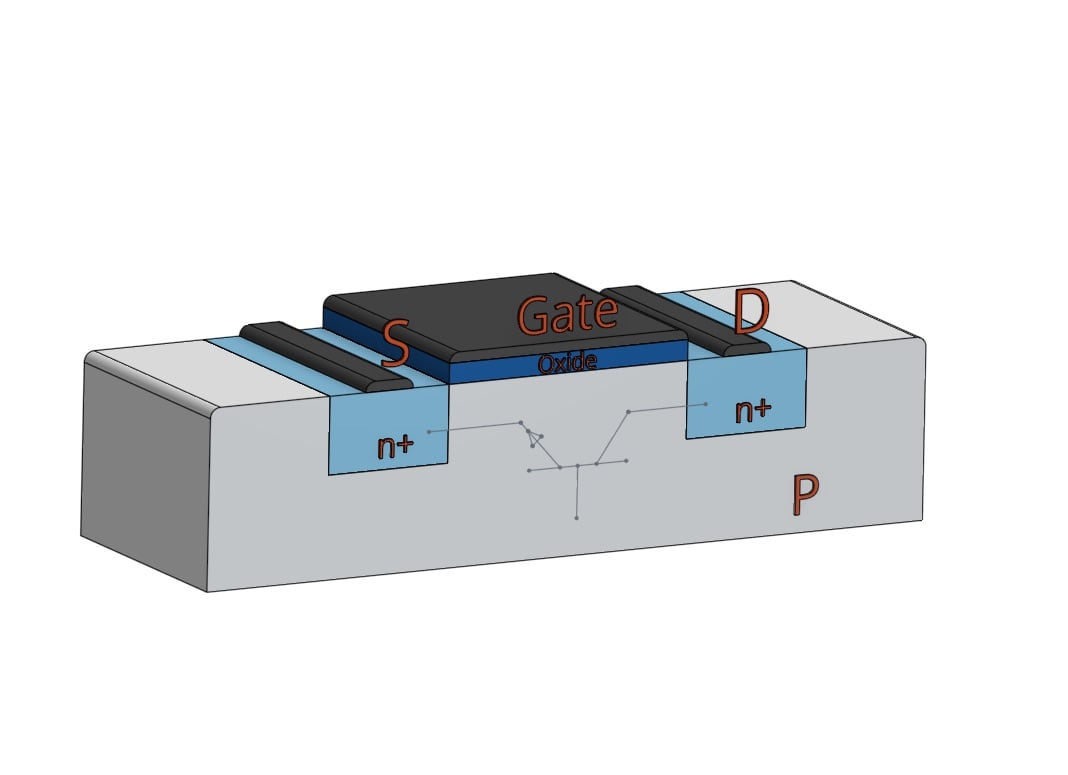

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions

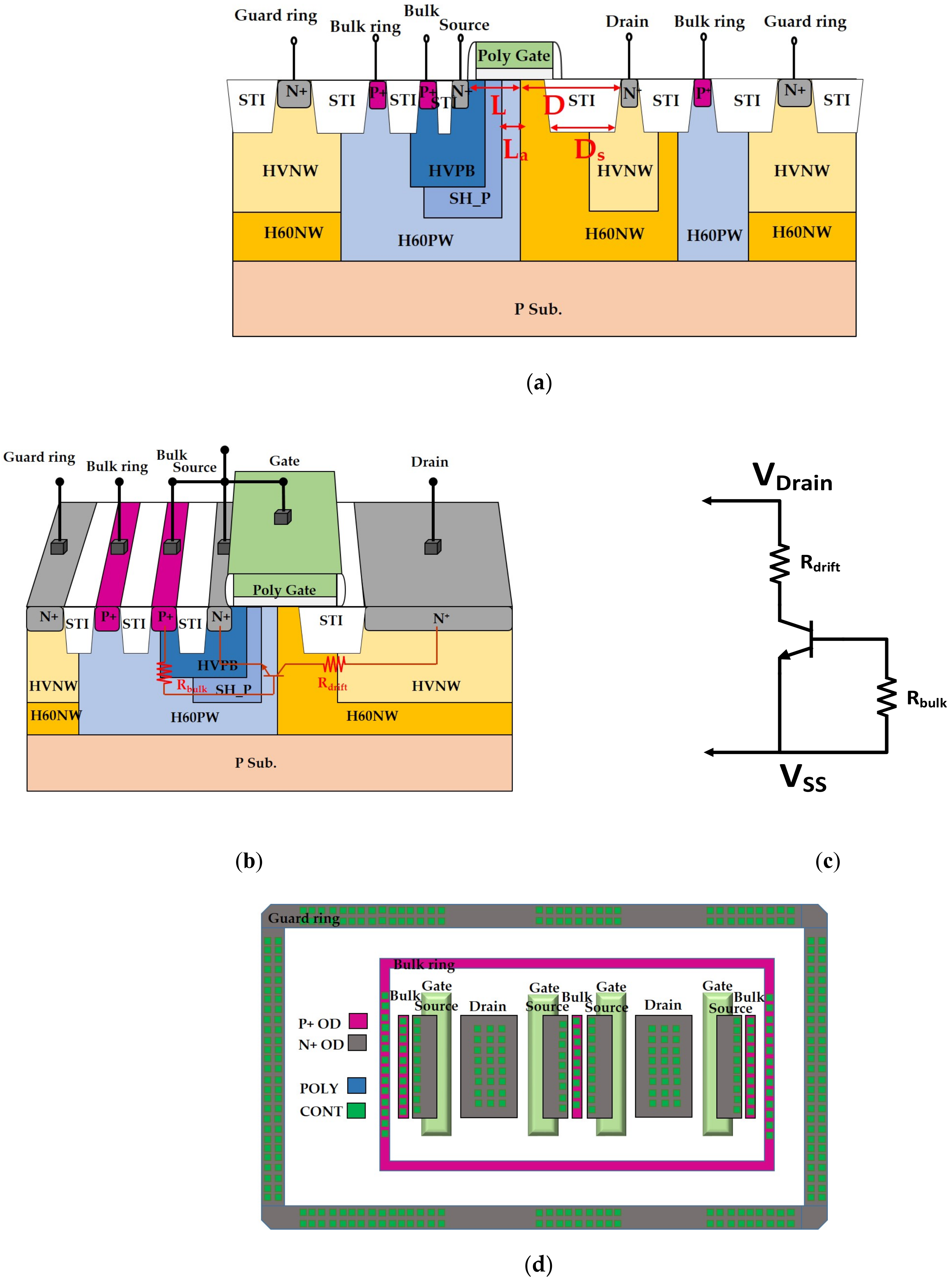

Electronics | Free Full-Text | Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs

Electronics | Free Full-Text | The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar